In a bid to meet the demand for compute GPUs and other processors used for AI and HPC, TSMC recently placed orders for additional tools used for chip-on-wafer-on-substrate (CoWoS) packaging, as indicated in the most recent earnings call. The company seems to be particularly optimistic about demand for AMD’s upcoming Instinct MI300-series datacenter APUs and GPUs, DigiTimes reports, saying it will be half of Nvidia's total output of CoWoS-packaged chips.

This ongoing expansion has been triggered by the upcoming mass production of AMD’s MI300 series and the persistent shortage of chip-on-wafer-on-substrate (CoWoS) packaging capacity, exacerbated by Nvidia’s demands. DigiTimes goes as far as saying, citing its sources in the industry, that when AMD’s MI300-series enters mass production, the volume of TSMC’s shipments for this CoWoS-based product will be equivalent to half of Nvidia’s CoWoS-equipped GPU total in a single quarter.

This essentially suggests that demand for AMD’s next-generation compute GPU will be half of Nvidia's shipments of CoWoS-equipped GPUs, which is a very optimistic expectation as today Nvidia commands over 90% of the compute GPU market due to the dominance of its CUDA software stack among AI and HPC developers.

To expand its CoWoS capacity, TSMC recently placed new orders with advanced packaging equipment suppliers, including Apic Yamada, Disco, Gudeng Precision Industrial, and Scientech, according to DigiTimes. Lead time for such tools is currently less than six months, according to China Renaissance Securities. In addition to AMD and Nvidia, Amazon, Broadcom, and Xilinx use CoWoS packaging for their data center offerings.

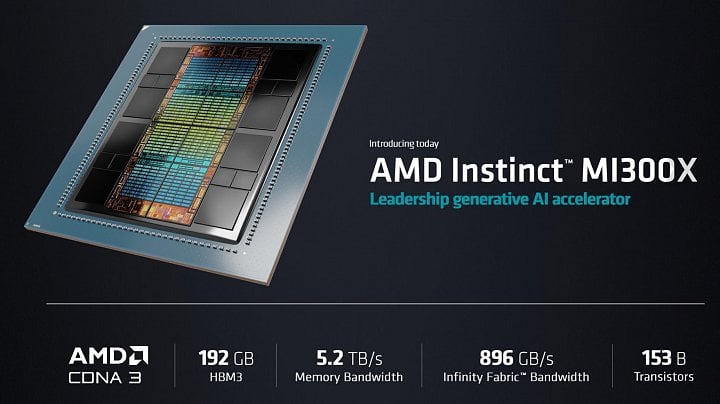

TSMC’s CoWoS packaging technology is used to stitch together Instinct MI250/MI300 chiplets as well as connect HBM memory to compute tiles of the solution. Without CoWoS packaging, it is impossible to build AMD’s MI200 and MI300-series products, as well as Nvidia’s compute GPUs that rely on HBM memory.

Based on unofficial information, TSMC intends to boost its existing CoWoS capacity from 8,000 wafers monthly to 11,000 wafers monthly by the conclusion of 2023. It then plans to further elevate this number to between 14,500 and 16,600 wafers by the end of 2024, another rumor suggests. Earlier, there were rumors suggesting that Nvidia aimed to expand its CoWoS capacity to 20,000 wafers per month by the close of 2024. Meanwhile, TSMC only says that it plans to double CoWoS capacity by the end of 2024.

AMD’s shares experienced a 4% uptick in after-hours trading on Tuesday, following the company’s announcement of ‘very high’ customer interest in its soon-to-be-launched Instinct MI300-series APU and GPU, which is set to enter production in the fourth quarter. However, the stock declined by approximately 6% on Wednesday, as analysts expressed doubts over the chip designer’s AI escalation goals, deeming them potentially overly optimistic, Reuters reports.

“Unless numbers get really material, soon, we fear estimates remain too high and the AMD stock looks a little stretched to us,” Bernstein analysts wrote in a note, according to Reuters.