Researchers from IBM, IMEC, Samsung, and TSMC will present their latest work on vertically-stacked complementary field-effect transistors (CFETs) at the upcoming International Electron Devices Meeting (IEDM) in December 2024, reports eeNewsEurope. CFET is usually seen as a successor to gate-all-around transistors that will enable future technology scaling, but the industry has yet to adopt GAA FETs for mass production.

The idea of CFETs, which stack n-type and p-type transistors on top of each other, was first proposed by the IMEC research institute in 2018. Even today, the actual implementation of CFET is still broadly in the field of research. According to IMEC's own roadmap, CFETs might reach widespread production by the A5 node, projected for around 2032 if everything goes well. Nonetheless, companies like Intel and TSMC began to demonstrate their advances in the field of CFETs in recent years, so it makes sense to take a look at what the IEDM brings.

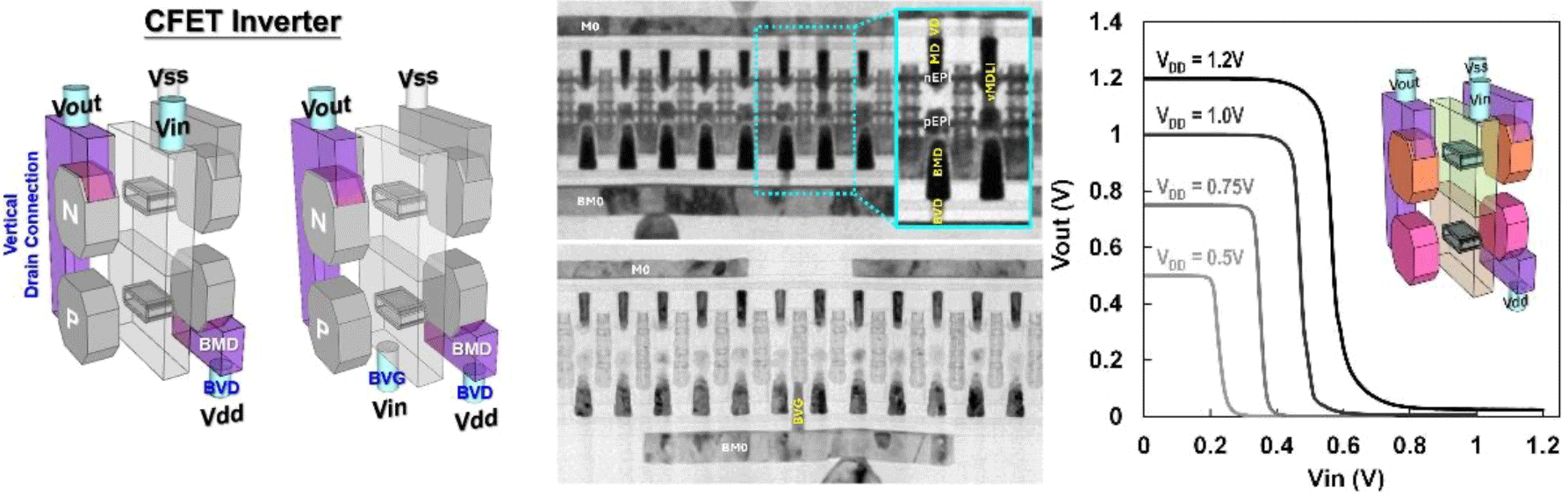

TSMC will discuss its development of a monolithic CFET inverter on a 48nm gate pitch, equivalent to a 5nm process. The inverter features stacked n-type and p-type nanosheet transistors with backside contacts and achieves a voltage transfer up to 1.2V and a subthreshold slope between 74 and 76mV/V for both transistor types. Although this marks a significant milestone, TSMC acknowledges that the technology is not ready for commercial production at present.

Key innovations of TSMC's design include a vertical drain-side local interconnect, a backside metalized drain (BMD), and a backside gate via (BVG), which collectively improve signal routing and optimize power, performance, and area (PPA).

Technically, this architecture provides a pathway for continued advancements in performance and power efficiency, as well as transistor density increases in the coming years. Still, TSMC's CFET advancements are in the lab and it will take years before they reach the company's fabs.

IBM Research and Samsung will present a 'Monolithic Stacked FET' that features a stepped channel design where lower channels are wider than upper ones, which reduces stack height and mitigates challenges associated with high aspect ratios. This research also covers isolation techniques for channels and source/drain areas, along with the use of dual work function metal. Details about metal or gate pitch will be revealed at the conference.

IMEC will present its work on a 'Double-Row CFET' designed to further scale CFETs both vertically and horizontally. IMEC believes that such transistor design could become viable at the 7a-class (7 angstroms) fabrication process, which is six or seven generations away. Interestingly, the 'Double-Row CFET' does not feature direct backside power contacts and they are explored with a 60nm gate pitch, similar to a 7nm node.

While the papers to be presented at the conference indicate that significant progress has been made in the CFET technology, such transistors are years away from mass production as challenges related to manufacturing complexity must still be overcome.

The IEDM conference will be held from December 7-11, 2024, in San Francisco, with recorded presentations accessible online afterward.