Rumors about TSMC having a silicon photonics program have been around for a long time, and at its Northern American Technology Symposium 2024, the company finally outlined its solution. The goal is to improve on-package connectivity, spanning all the way to 12.8 Tbps of bandwidth.

"As we bring more computational capability into the mass packaging, data transfers become a challenge, but we find ourselves often limited by the I/O vendors," said Kevin Zhang, Vice President of Business Development at TSMC. "At TSMC, we have spent many, many years working on silicon photonics. We have the capability to bring silicon photonics close to the switching elements in order to create a very energy efficient high-speed signaling to address the future computation requirement."

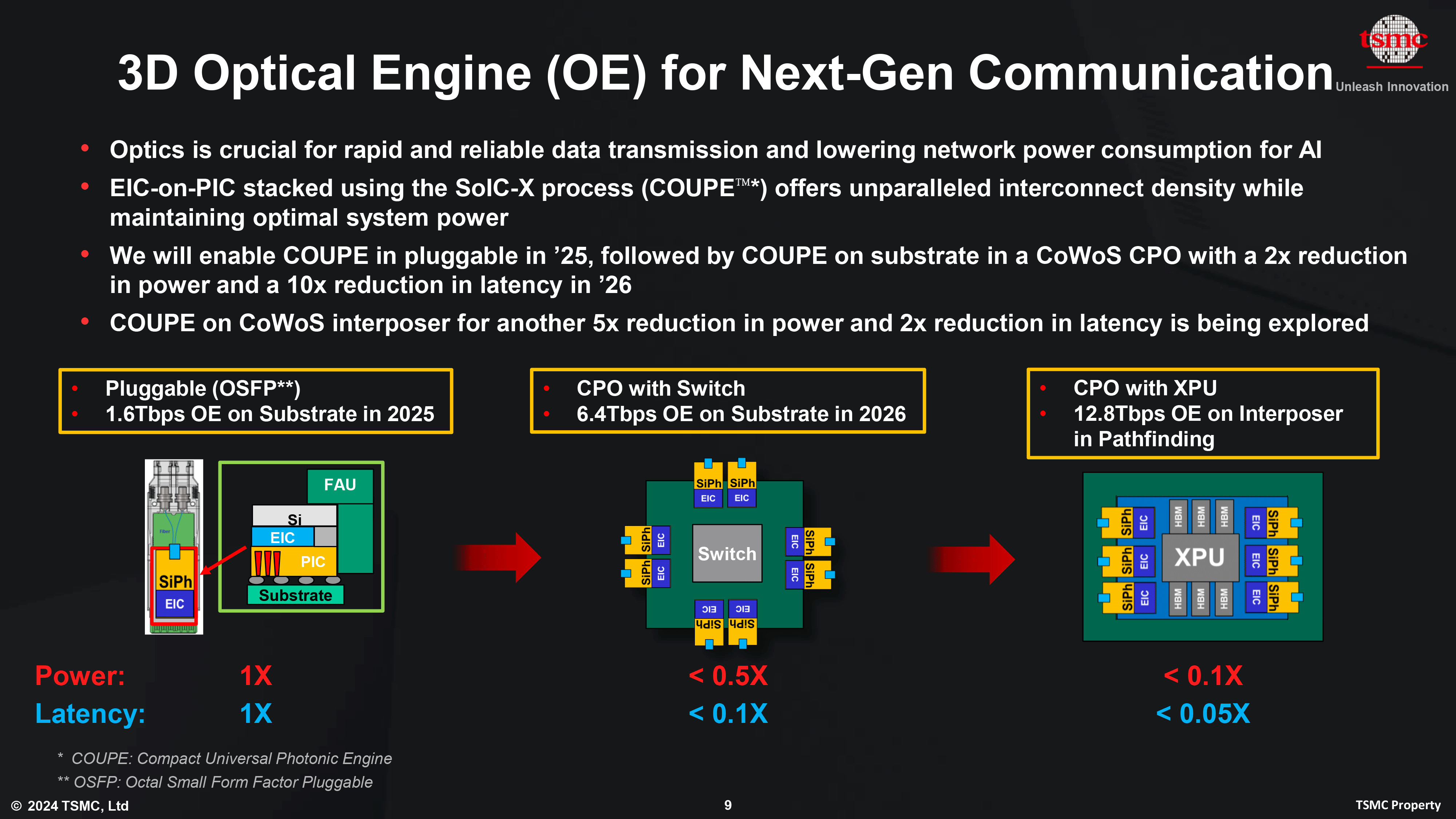

Silicon photonics is set to be a game-changer for future datacenters due to increasing bandwidth demands that copper signaling just cannot meet. TSMC's silicon photonics technology relies on the Compact Universal Photonic Engine (COUPE) that combines a 65nm electronic integrated circuit (EIC) with a photonic integrated circuit (PIC) using the company's SoIC-X packaging technology. TSMC claims that its SoIC-X interconnection has very low impedance, which means that COUPE is very efficient in terms of power usage.

The development trajectory of COUPE has three major phases. TSMC's first silicon photonics product is an optical engine for OSFP connectors (Octal Small Form Factor Pluggable) that features a data transfer rate of 1.6 Tbps, twice the maximum of current top-tier copper Ethernet solutions. This initial iteration promises not just superior bandwidth but also improved power efficiency, addressing two critical concerns in modern datacenters. Subsequent generations of COUPE aim to push the boundaries further.

The second generation silicon photonics will integrate COUPE into CoWoS packaging (Chip on Wafer on Silicon) and features co-packaged optics with a switch. This will enable motherboard-level optical interconnections with speeds of up to 6.4 Tbps.

The third generation targets transfer rates of up to 12.8 Tbps and is designed to be integrated into processor packaging. This iteration is still in the exploratory phase, with no definite release timeframe. TSMC says it's looking at further reductions in power use and latency.

TSMC's strategic pivot into the silicon photonics market, previously dominated by companies like GlobalFoundries, indicates a significant shift in the competitive landscape. By deploying its 3D Optical Engine, TSMC not only enters a crucial datacenter connectivity field, but it plans to significantly reduce power consumption of silicon photonics technology. This could significantly impact future chip designs, particularly in the area of AI workloads where communication is becoming a significant bottleneck.