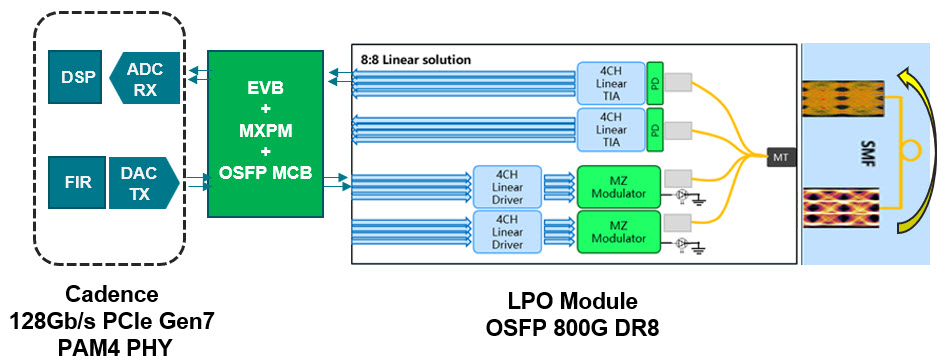

Cadence demonstrated its proprietary optical connectivity solution for PCIe 7.0 at the PCI-SIG DevCon 2024 earlier this month. The world's first demonstration of 128 GT/s PCIe 7.0 interconnection over optics is largely a proof-of-concept as the PCIe 7.0 specification is yet to be finalized. However, having a working optical connectivity solution for a standard that is set to be used towards the end of the decade clearly demonstrates Cadence's technical prowess.

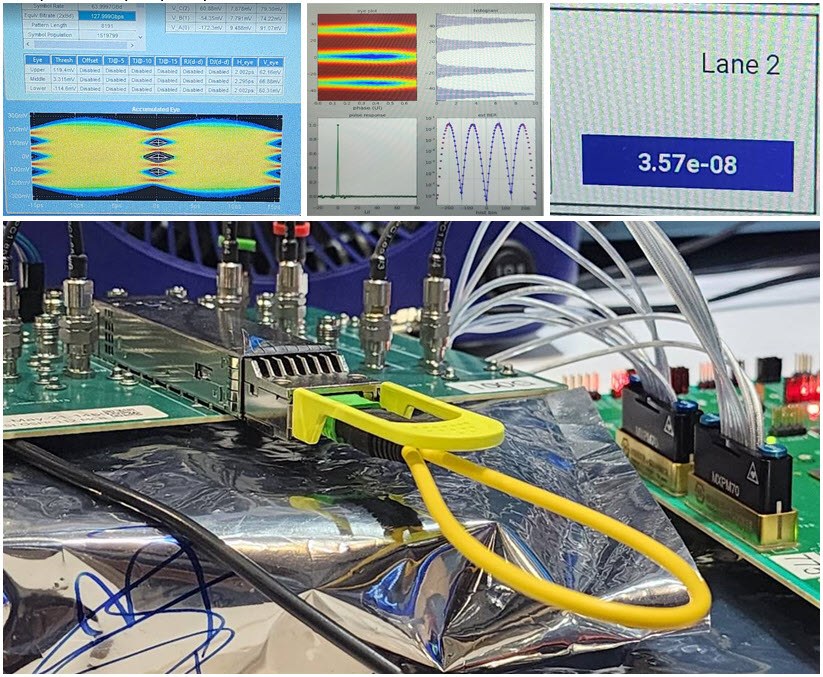

During the event, Cadence demonstrated its 128 GT/s PCIe 7.0 IP's transmission and reception capabilities using a real-world, low-latency, non-retimed, linear optical connection. This setup consistently achieved a pre-FEC BER of ~3E-8, well within the PCIe specification requirement of 1E-6, making it the first stable demonstration of 128 GT/s over standard optical connectors. The receiver Eye PAM4 histograms, depicted on an image demonstrated by Cadence, exhibit excellent linearity and margin.

Back in August last year PCI-SIG formed its Optical Workgroup, which will work on industry-standard PCIe over optical interfaces. To this day, PCI Express has relied solely on copper interconnections.

However, because PCIe interconnections are getting longer in applications like AI and HPC servers and usage of retimers is both complicated, expensive and power consuming as well as having its limitations (as only two retimers per link can be used). Therefore, the decision to explore optical connectivity is certainly an important one.

Just like Cadence, there are several other vendors currently provide proprietary external PCIe connectivity solutions. This does not necessarily contradict PCI-SIG's plan to standardize optical PCIe connectivity, as the development of an optical standard seeks to establish a unified approach for PCIe over fiber optics. PCI-SIG emphasized that it is not creating a standard for any specific optical technology, but aims to develop a technology-agnostic specification that supports a broad spectrum of optical technologies.

An optical solution for PCIe 7.0 is something that will be required in the years to come. But Cadence showcased quite a number of PCIe setups, including PCIe 7.0 electrical, and various PCIe 6.0 configurations at the event. These included RP/EP interop back-to-back setups, protocol demonstrations in FLIT mode at both the Cadence and Lecroy booths, JTOL testing with Anritsu and Tektronix equipment, and system-level interoperability demos with a PCIe Gen5 platform at the SerialTek booth.