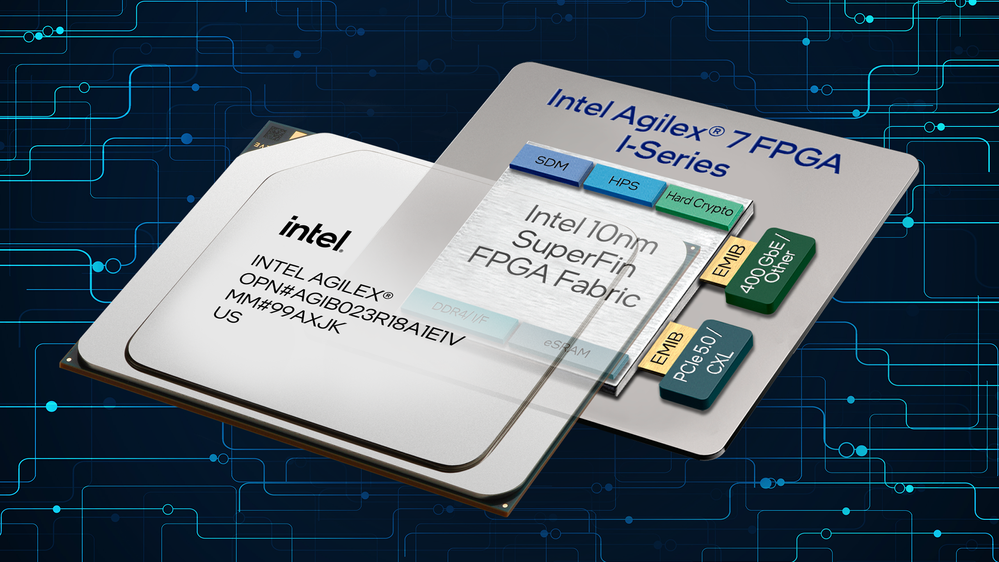

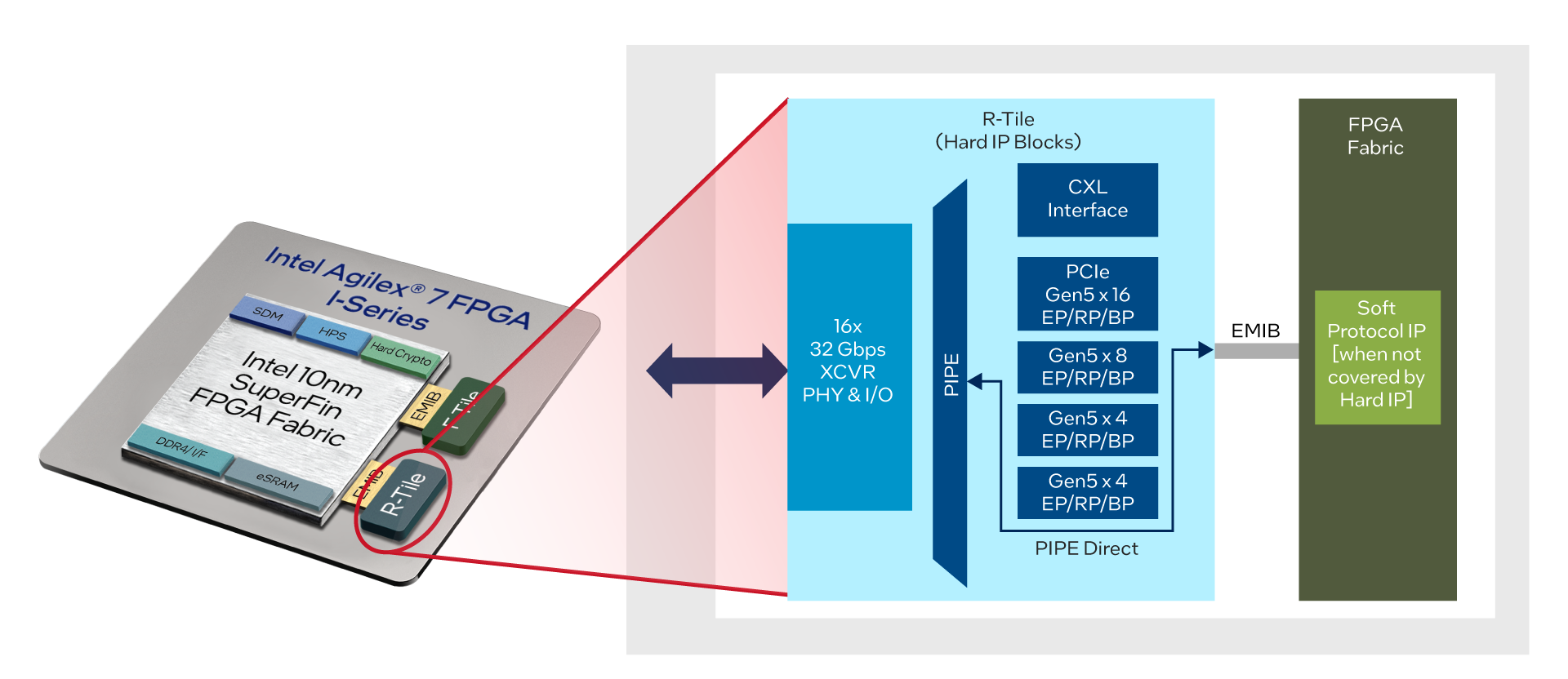

Intel today announced its Agilex 7 M-Series family of Field-Programmable Gate Array (FPGA) products, doubling down on its revitalized 10nm SuperFin fabrication node. Citing rising market demand for FPGA solutions as co-processors for Networking, Data Center, High Performance Computing (HPC)Cloud computing and other applications, Intel promises increased flexibility (mainly due to FPGA's inherently programmable nature) and higher scaling capabilities than ever before. Intel's Agilex 7 FPGAs introduce a new chiplet as part of their heterogeneous multi-die architecture, the R-Tile, which is responsible for delivering the latest connectivity technologies - namely PCIe 5.0 and CXL support - in hardware-accelerated, hard-coded IP blocks.

The new heterogeneous R-Tile chiplet is the star of the show for Intel, allowing it to claim the title of the only FPGA family that carries certification for the full PCI-SIG 5.0 x16 data rate. Xilinx, which is now folded into AMD, would be an example of another leading-edge FPGA developer, so there's the feeling of a race won for Intel here.

Interestingly, Intel seems to be doubling down on a separation between FPGA and CPU products. Perhaps that's a result of its earlier inroads into integration, of which only silicon ghost stories remain. AMD seems to be much more confident it's cracked the case: the company is seemingly looking to incorporate FPGA capabilities into the company's EPYC CPUs as early as this year. Now, that doesn't cement a departure between both companies - AMD may be also looking at a chiplet-like integration, whether vertically via 3D stacking or by incorporating segregated FGPA-specific IP in a separate chip.

The general idea of FPGAs is their inherent flexibility, which allows developers to quickly iterate on circuit arrangement and processing blocks to adapt the FPGA for the specific workloads at hand. Being more specialized hardware, FPGAs can be used to accelerate workloads that aren't CPU-dependent, thus freeing up valuable CPU resources for their specific tasks (such as spinning out VMs in a cloud-based installation) instead of tapping into their lower power efficiency (the cost of their generalized processing capabilities).

Intel's R-Tile essentially brings the hardware-accelerated IP blocks responsible for handling the PCIe 5.0 and CXL 1.1/2.0 protocols into its Agilex 7 FPGA family. That should bring about significant improvements in power efficiency and data throughput, which are important elements to lower Total Cost of Ownership (TCO) for high-performance installations. But with these choices, there are always trade-offs: Intel is adding yet another fixed-function hardware block onto a product whose desirability lies in it being programmable. Programmable die area is the FPGA buyer's mantra, after all.

It also bears mentioning that as a product, R-Tile is specifically saying "I'm here to reduce the load on your CPUs while delivering increased performance". But another answer to that need isn't about moving CPU functions towards an FPGA; it's to merely increase the number of available CPU resources. And that could be done with more CPUs (which might make sense to some installers) or additional CPU cores. Intel's Agilex 7 M-Series is specifically marketed to Intel's 4th Gen Scalable Xeons, after all, and those aren't the core-count kings in any shape.

Intel's bet is that the questions above have an answer, and that it knows the answer: that's why it introduced Agilex 7. Intel's answer is that consumers want to remove CPU overhead by moving it onto an FPGA packaging. They want the best performance/watt possible (one of the highest contributors to high TCO cost), so they'll move things to where they're fastest. Luckily, this move benefits Intel in other ways. For the company, it's a matter of its own efficiency - and as such, a matter of cost.

That's where Intel's embedded multi-die interconnect bridge (EMIB) really shines. As the proverbial "glue" holding the disparate processing blocks together, EMIB allows Intel to further separate IP blocks at the manufacturing level, increasing die efficiency and reducing the overall cost-per-wafer (and resulting cost-per-chip) equation.

For the consumer, it also theoretically lowers costs: Intel (and the industry's) dream is to be able to mix and match different hardware IP blocks (from the same vendor, or even multiple vendors and manufacturing processes), meaning that customers need only pay for the silicon they'll actually use, with the specs they'll actually use. In a sense, this would make every chip an FPGA.

With all that in mind, it's possible today's Agilex 7 with R-Tile is as much a new FPGA product as it is a new staple on Intel Foundry Services' (IFS) catalog. Either way, it moves Intel in the direction it wants - and needs - to go. And that's just good business.