We are currently in the midst of a global semiconductor shortage that is negatively impacting the entire technology supply chain. With multiple markets struggling to source chips and other related materials, the supply of everything from automobiles to graphics cards for PC gaming is too thin to meet demand and prices have skyrocketed. As detrimental as the current semiconductor shortage is, however, another challenging shortage may be looming, and it’s one that could stall development and innovation of new chips and processors worldwide, without a sea change in how chips are designed. Synopsys CEO Aart de Geus, however, believes his company and its advanced AI design automation tools may have an answer.

Pundits have been proclaiming the death of Moore’s Law for many years. For the uninitiated, Moore’s Law is an observation made by Intel Co-Founder Gordon Moore, that says the number of transistors in an integrated circuit (IC) doubles approximately every two years. After about the third decade or so, every time I hear about the “death of Moore’s Law” at industry events, I (and about half of the other analysts and journalists in the room) roll our eyes. But the fact remains that Moore’s Law has plateaued, as chip makers strive for more advanced process nodes, while chip complexity has also increased exponentially.

SysMoore: Leveraging Systemic Technology Advancement Beyond The Transistor

Compounding this reality, the number of engineers working to solve the current design problems associated with Moore’s Law has not commensurately increased. This situation has revealed systemic issues with the dynamics of the traditional interpretation of Moore’s Law. The challenges presented to today’s chip makers aren’t solely related to the number of transistors being squeezed into the chip being designed. There are new opportunities to leverage and advance systemic complexity in addition to traditional Moore’s Law advancements. This “SysMoore” era, as de Geus puts it, needs new tools and strategies to continue pushing the industry forward, at the pace necessary to address the growing needs of manufacturers and industries – both large and small – with the seemingly insatiable demand to make new products as “smart” as possible.

Aart de Geus explained that the industry’s central challenge is how to achieve 1000X AI compute from cloud to edge in the next decade. That means more quickly building better chips, at a lower costs, and he proposes that AI tools are the key, game-changing disruption that’ll make it possible. Synopsys recently demonstrated how a problem that had previously taken months of work by an entire design team could be accomplished with superior results in just a few weeks by a single engineer.

Aart is referencing his company’s tool called DSO.ai. Synopsys claims DSO.ai (Design Space Optimization AI) is the world’s first autonomous AI tool set for chip design. There’s probably some nuance in that claim because semiconductor giants like NVIDIA and Intel have been using AI to assist with chip design for some time now, though Synopsys doesn’t make its own chips. Rather, Synopsys empowers its customers to produce their products with advanced chip design tools, verification tools and services, IP integration, and software security and quality testing.

It's Not Science Fiction, AI Is Designing AI Chips

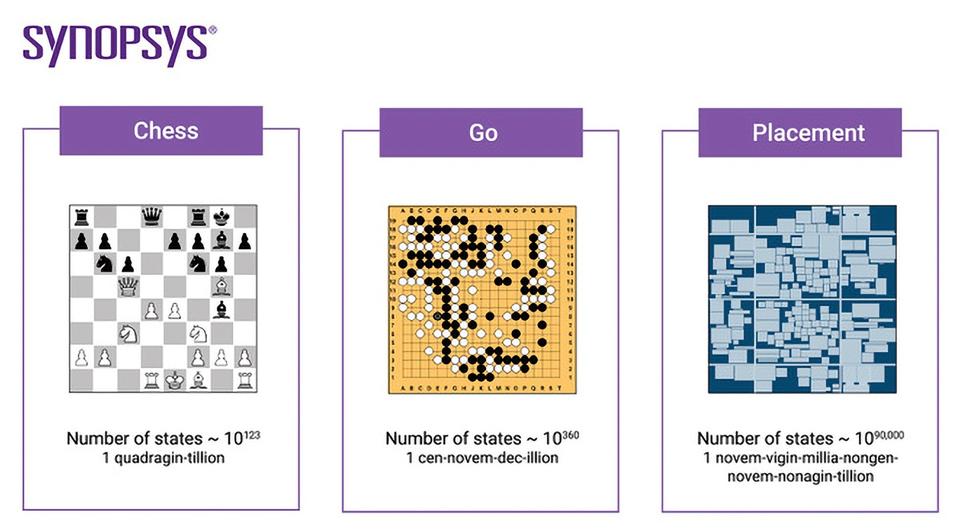

Synopsys claims its DSO.ai tool can dramatically accelerate, enhance and reduce the costs involved with something called place-and-route. Place-and-Route is an integral stage in the design of circuit boards, ICs, and FPGAs (Field Programmable Gate Arrays). Just as it sounds, place-and-route (sometimes called PnR or Floorplan Placement) referrers to the placement of logic and IP blocks, and the routing of the traces and various interconnects designed to join them all together. Although various criteria are also top of mind throughout other stages in the design cycle of a chip, power, frequency, latency and silicon area are all important considerations during place-and-route, within the strict confines of the specific manufacturing process being employed. Synopsys’ DSO.ai optimizes and streamlines this process using the iterative nature of artificial intelligence and machine learning, to turn what used to take dozens of engineers weeks or potentially months, into something a junior engineer can do on their own in just days. DSO.ai iterates on the floorplan and layout of a chip, and learns from each iteration, fine tuning and optimizing the chip within its design parameters along the way. Not only does this positively impact the economics and success rate of chip design, but results in a fundamental shift in design resources and methodology, which liberates engineers that may have been previously occupied by place-and-route duties to address and be more creative in other aspects of cutting-edge chip design.

During discussions with de Geus, he further explained that he didn’t expect to see the world’s pool of engineers increase by 1000X anytime soon, and scaling engineers with the diverse skillsets and knowledge necessary to do things like architecture exploration is a harsh reality that won’t be alleviated anytime soon. But he also believes that AI tools are bridging the gap — so designing a custom AI processor is now a possibility for even the smallest design teams. By offloading mundane tasks from chip architects, they can begin solving higher abstraction level challenges. Perhaps a more important point he makes is that many of the systemic complexity challenges the industry is facing today cannot be solved by human capabilities alone, no matter how many engineers are thrown at the problem. In essence, artificial intelligence is going to be required to compensate for the shortage of human intelligence.

Everything Is Getting Smarter And AI Is Enabling Us To Do Much More

AI isn’t just a buzzword any longer. AI is being used everywhere from silly photo filters in phone apps, to recommendation engines, autonomous vehicles, big data analytics and advanced design automated design tools like DSO.ai. Specialized chips with dedicated AI processors reside almost everywhere including your smartphone, computers, and the in latest automotive tech. Now, the chip industry itself has reached a stage where AI is aiding in the design of these AI chips, and it is enabling engineering teams of all sizes to compete at the relentless pace required in the semiconductor industry.

“With Classic Moore’s Law, we saw an unbelievable push in scale complexity that finally made AI possible. Now every vertical market seeks to extract economic value from their data by making everything smart. This has created a pull on the semiconductor industry to deliver another 1000X to tackle the systemic complexity that ‘smart everything’ creates. But 1000X means overcoming levels of design complexity that far exceed human engineering capability and economic means today”, de Geus said.

Renowned engineer Jim Keller recently said, “It’s a bloody miracle; ten years ago you couldn’t do a hardware startup”. Keller was referencing advancements in design automation by Synopsys (and others) that have altered the economics and manpower necessary to launch innovative hardware startups. And back in March, NUVIA – a young company with approximately 100 engineers – was acquired by Qualcomm for $1.4B. This illustrates what’s currently possible with these powerful new chip design tools and intelligent strategies. The old semiconductor paradigms are rapidly becoming a thing of the past. Today, it’s about the best transistors, architectures, and accelerators for the job, and the human-constrained physical design engineering effort no longer has to be a gating factor.